- Retrait en 2 heures

- Assortiment impressionnant

- Paiement sécurisé

- Toujours un magasin près de chez vous

- Retrait gratuit dans votre magasin Club

- 7.000.0000 titres dans notre catalogue

- Payer en toute sécurité

- Toujours un magasin près de chez vous

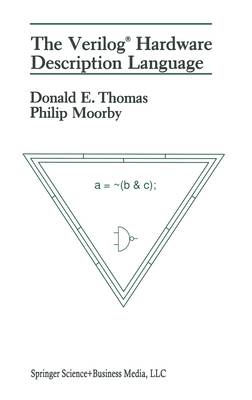

Veriloga (R) Hardware Description Language

D E Thomas, Donald E Thomas, Philip R Moorby

Livre relié | Anglais

151,45 €

+ 302 points

Description

1. Verilog - A Tutorial Introduction.- 1.1 Describing Digital Systems.- 1.2 Getting Started.- 1.2.1 A Structural Description.- 1.2.2 Simulating the NAND Latch.- 1.3 Module Hierarchy.- 1.3.1 The Counter.- 1.3.2 Components of the Counter.- 1.3.3 A Clock for the System.- 1.3.4 Tying the Whole Circuit Together.- 1.4 Behavioral Modeling.- 1.4.1 A Behavioral Model of the m16 Counter.- 1.4.2 Mixing Structure and Behavior.- 1.4.3 Assignment Statements.- 1.4.4 Mixing Behavioral and Structural Descriptions.- 1.5 Summary.- 1.6 Exercises.- 2. Behavioral Modeling Constructs.- 2.1 Process Model.- 2.2 If-Then-Else.- 2.2.1 Where Does The ELSE Belong?.- 2.2.2 The Conditional Operator.- 2.3 Loops.- 2.3.1 Four Basic Loop Statements.- 2.3.2 Exiting Loops on Exceptional Conditions.- 2.4 Multi-way branching.- 2.4.1 If-Else-If.- 2.4.2 Case.- 2.4.3 Comparison of Case and If-Else-If.- 2.4.4 CaseZ and CaseX.- 2.5 Functions and Tasks.- 2.5.1 Tasks.- 2.5.2 Functions.- 2.5.3 A Structural View.- 2.6 Summary.- 2.7 Exercises.- 3. Concurrent Process Statements.- 3.1 Concurrent Processes.- 3.2 Events.- 3.2.1 Event Control Statement.- 3.2.2 Named Events.- 3.2.3 An Example of Hierarchical Names.- 3.3 The Wait Statement.- 3.3.1 A Complete Producer-Consumer Handshake.- 3.3.2 Comparison of the Wait and While Statements.- 3.3.3 Comparison of Wait and Event Control Statements.- 3.4 Disabling Named Blocks.- 3.5 Quasi-continuous assignment.- 3.6 Sequential and Parallel Blocks.- 3.7 Exercises.- 4. Logic Level Modeling.- 4.1 Introduction.- 4.2 Logic Gates and Nets.- 4.2.1 Modeling Using Primitive Logic Gates.- 4.2.2 Four-Level Logic Values.- 4.2.3 Nets.- 4.2.4 Module Port Specifications.- 4.3 Continuous Assignment.- 4.3.1 Behavioral Modeling of Combinational Circuits.- 4.3.2 Net and Continuous Assign Declarations.- 4.4 Parameterized Definitions.- 4.5 Logic Delay Modeling.- 4.5.1 A Gate Level Modeling Example.- 4.5.2 Gate and Net Delays.- 4.5.3 Minimum, Typical, and Maximum Delays.- 4.6 Delay Paths Across a Module.- 4.7 Summary.- 4.8 Exercises.- 5. Defining Gate Level Primitives.- 5.1 Combinational Primitives.- 5.1.1 Basic Features of User-Defined Primitives.- 5.1.2 Describing Combinational Logic Circuits.- 5.2 Level- and Edge-Sensitive Sequential Primitives.- 5.2.1 Level-Sensitive Primitives.- 5.2.2 Edge-Sensitive Primitives.- 5.3 Shorthand Notation.- 5.4 Mixed Level- and Edge-Sensitive Primitives.- 5.5 Summary.- 5.6 Exercises.- 6. Switch Level Modeling.- 6.1 A Dynamic MOS Shift Register Example.- 6.2 Switch Level Modeling.- 6.2.1 Strength Modeling.- 6.2.2 Strength Definitions.- 6.2.3 An Example Using Strengths.- 6.2.4 Resistive MOS Gates.- 6.3 Ambiguous Strengths.- 6.3.1 Illustrations of Ambiguous Strengths.- 6.3.2 The Underlying Calculations.- 6.4 Summary.- 6.5 Exercises.- 7. Two Large Examples.- 7.1 The miniSim Example.- 7.1.1 Overview.- 7.1.2 The miniSim Source.- 7.1.3 Simulation Results.- 7.2 The 8251A Example.- 7.2.1 Overview.- 7.2.2 The 8251A Source.- 7.3 Exercises.- Appendix A. Lexical Conventions.- A.1 White Space and Comments.- A.2 Operators.- A.3 Numbers.- A.4 Strings.- A.5 Identifiers, System Names, and Keywords.- Appendix B. Verilog Operators.- B.1 Table of Operators.- B.2 Operator Precedence.- B.3 Operator Truth Tables.- B.3.1 Bitwise AND.- B.3.2 Bitwise OR.- B.3.3 Bitwise XOR.- B.3.4 Bitwise XNOR.- B.4 Expression Bit Lengths.- Appendix C. Verilog Gate Types.- C.1 Logic Gates.- C.2 BUF and NOT Gates.- C.3 BUFIF and NOTIF Gates.- C.4 MOS Gates.- C.5 Bidirectional Gates.- C.6 CMOS Gates.- C.7 Pullup and Pulldown Gates.- Appendix D. Registers, Memories, Integers, and Time.- D.1 Registers.- D.2 Memories.- D.3 Integers and Times.- Appendix E. System Tasks and Functions.- E.1 Display and Write Tasks.- E.2 Continuous Monitoring.- E.3 Strobed Monitoring.- E.4 File Output.- E.5 Simulation Time.- E.6 Stop and Finish.- E.7 Random.- Appendix F. Formal Syntax Definition.- F.1 Source Text.- F.2 Declarations.- F.3 Primitive Instances.- F.4 Module Instantiations.- F.5 B...

Spécifications

Parties prenantes

- Auteur(s) :

- Editeur:

Contenu

- Nombre de pages :

- 244

- Langue:

- Anglais

Caractéristiques

- EAN:

- 9780792391265

- Date de parution :

- 31-12-90

- Format:

- Livre relié

- Format numérique:

- Genaaid

- Dimensions :

- 156 mm x 234 mm

- Poids :

- 517 g

Seulement chez Librairie Club

+ 302 points sur votre carte client de Librairie Club

Les avis

Nous publions uniquement les avis qui respectent les conditions requises. Consultez nos conditions pour les avis.